First MIPS-based, FPGA-optimised soft core processor. 10 May 2011 Altera, MIPS Technologies and SLS have just announced the MP32 core.

Altera Corporation, MIPS Technologies, and System Level Solutions Corporation have introduced a MIPS-based, FPGA-optimised soft processor for use on Altera’s FPGA and ASIC devices. The MP32 processor is a MIPS compatible applications class processor that inherits one of the largest ecosystems of software development tools and operating system support in the industry. It is the industry’s first FPGA-based soft processor supported by Wind River’s VxWorks RTOS and the MIPS Navigator ICS software development suite. When combined with Altera’s portfolio of embedded intellectual property cores, innovative FPGA design tools and a portfolio of programmable logic devices, the MP32 processor is suitable for the development of flexible, single-chip solutions used in networking, video and digital signal processing applications. The MP32 processor is distributed and supported through Altera Embedded Alliance partner SLS.

Soft_core_processors. OpenCores. Details Name: avr_core Created: Nov 5, 2002 Updated: Feb 4, 2014 SVN Updated: Oct 28, 2012 SVN: Browse Latest version: download Statistics: View Other project properties Category: Processor Language: Development status: Stable Additional info: none WishBone Compliant: No License: Description Microcontroller core compatible with one used in AT mega 103 and written in VHDL.

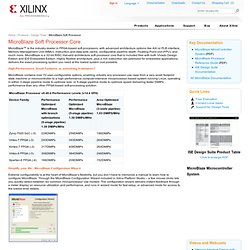

Features • Core features: – 32 x 8 general purpose registers – Twenty three interrupt vectors – Supports up to 128 Kb of program and up to 64 Kb of data memory • Peripheral features: – Programmable UART – Two 8-bit Timer/Counters with separate prescalers and PWM – Eight external interrupt sources – Two parallel ports Status The core was tested with several ASM and C programs. OpenRISC Overview. MicroBlaze Soft Processor. MicroBlaze Soft Processor Core MicroBlaze™ is the industry-leader in FPGA-based soft processors, with advanced architecture options like AXI or PLB interface, Memory Management Unit (MMU), instruction and data-side cache, configurable pipeline depth, Floating-Point unit (FPU), and much more.

MicroBlaze is a 32-bit RISC Harvard architecture soft processor core that is included free with both Vivado Design Edition and IDS Embedded Edition. Highly flexible architecture, plus a rich instruction set optimized for embedded applications, delivers the exact processing system you need at the lowest system cost possible. High-Performance, Small Footprint, or something In-between? Simplify your life - MicroBlaze Configuration Wizard Extreme configurability is at the heart of MicroBlaze’s flexibility, but you don’t have to memorize a manual to learn how to configure MicroBlaze. New version 8 features expand MicroBlaze capabilities even further. PicoBlaze. PicoBlaze is the designation of a series of three free soft processor cores from Xilinx for use in their FPGA and CPLD products.

They are based on an 8-bit RISC architecture and can reach speeds up to 100 MIPS on the Virtex 4 FPGA's family. The processors have an 8-bit address and data port for access to a wide range of peripherals. The license of the cores allows their free use, albeit only on Xilinx devices, and they come with development tools. Third party tools are available from Mediatronix and others. Also PacoBlaze, a behavioral and device independent implementation of the cores exists and is released under the BSD License. The PicoBlaze design was originally named KCPSM which stands for "Constant(K) Coded Programmable State Machine" (formerly "Ken Chapman's PSM"). Instantiation[edit] When instantiating a PicoBlaze microcontroller in VHDL, the respective KCPSM component name must be used.[2] For example, for a PicoBlaze3 processor: Performance[edit] Architectural notes[edit]

MicroBlaze. The MicroBlaze is a soft processor core designed for Xilinx FPGAs from Xilinx.

As a soft-core processor, MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs. Overview[edit] Many aspects of the MicroBlaze can be user configured: cache size, pipeline depth (3-stage or 5-stage), embedded peripherals, memory management unit, and bus-interfaces can be customized. The area-optimized version of MicroBlaze, which uses a 3-stage pipeline, sacrifices clock-frequency for reduced logic-area. The performance-optimized version expands the execution-pipeline to 5-stages, allowing top speeds of 210 MHz (*on Virtex-5 FPGA family.) With the memory management unit, MicroBlaze is capable of hosting operating systems requiring hardware-based paging and protection, such as the Linux kernel. EDK[edit] The SDK handles the software that will execute on the embedded system. Open Source[edit] In May, 2009, Edgar E.

Embedded Processor. Nios II. Nios II is a 32-bit embedded-processor architecture designed specifically for the Altera family of FPGAs.

Nios II incorporates many enhancements over the original Nios architecture, making it more suitable for a wider range of embedded computing applications, from DSP to system-control. Nios II is comparable to MicroBlaze, a competing softcore CPU for the Xilinx family of FPGA. Home - Aeroflex Gaisler. OpenSPARC T1 processor.