Logic Analyzer Software Review « irq5.io. I was looking into the Openbench Logic Sniffer (OLS) client, an open source logic analyzer software to be used with the Logic Sniffer from Dangerous Prototypes and Gadget Factory, so I thought it might be worthwhile to look at other alternatives, including commercial products.

In the next few posts, it will probably become obvious why I’m doing this. Since I do not have any of the hardware, I must make it clear that I am only reviewing the software that is meant to be used with their analyzers. Good logic analyzer products will usually make their software available free, with either some demo files or a means to generate random or test waveforms. Written in C++, Qt. Runs on Windows, Mac and Linux. Zooming in and out is achieved by clicking or right-clicking in the waveform window, respectively. Random data generation (simulation). SUMP compatible Arduino based logic analyzer. Hello everyone.

I work in Silicon Valley in the networking field and electronics are just a hobby. Coreboot developer blogs. I got the sump.org Logic Analyzer running on a Xilinx Spartan-3E FPGA starter kit board.

This wasn't too difficult, but there were some annoying problems that I'll share with you. Buying the board The particular board is not sold by Xilinx anymore, but the company that actually designed the board for Xilinx, Digilent Inc., still sell it. Installing and setting up the tools Once again I downloaded and installed the 32-bit ISE WebPack 11.1 software on 32-bit Linux. Logic Analyzer Software Review « irq5.io. Testing MPLABX and Open Bench Logic Analyzer (part-2) The previous post is about the installation, developing and programming of logic analyzer testing circuit with MPLABX.

Now, it is time to test with my new OBLS. Connect all input test connectors with PIC PORTB pins and also ground. Power up the circuit. First, I tested the circuit with oscilloscope to sure the code and circuit are working. Good, output signals are generating. World’s Simplest Logic Analyzer for $5. Today’s post documents my recent hack that may just be the world’s simplest logic analyzer.

More accurately, it is a circuit consisting of a 74HC126 quad buffer chip and R-2R resistor network (eleven 330 ohm resistors) that acts as a D/A converter, enabling one to analyze four logic lines with a single channel digital oscilloscope and $5 in parts! With the circuit described below and an entry level USB scope like the PicoScope 2204, bursts of data can be captured at 10 MSps (million samples per second), and continuous capture rates of 2.5 MSps are possible, the length of the capture only limited by your PC’s memory. This is obviously much better than recently covered Bus Pirate’s 1 MSps for 4 ms! Even higher throughput can be achieved with better scopes, although the A/D conversion requires several consecutive samples at same logic level, which means that a 100 MHz scope with 200 MSps capture rate should generally be able to analyze logic operating at ~40 MHz speeds.

Logic Analyzer Client. The Java client should run on most platforms for which JRE 1.4.2 or newer and the RXTX package exist.

This means it should work with Linux, Windows, Solaris and many more. The client allows to configure the device, read and display captured data and to perform file operations on captured data. It can be extended with plugins and some classes can be reused for own applications. See the developer documentation for details: API Documentation 3rd Party Packages RXTX - Provides access to serial ports (required) PgsLookAndFeel - Provides the look and feel seen below (optional) Screenshots of Version 0.8 The new I2C protocol analyzer:

Prototype: Openbench Logic Sniffer logic analyzer. The most recent documentation is now on the wiki Openbench Logic Sniffer is an open source logic analyzer.

It’s designed to support the SUMP logic analyzer software at the lowest possible cost. Download the source and design files from the Gadget Factory project page. This project started in the comments on a post. Initial circuit design, PCB layout, development, and testing continued in the forum under the code name Project SUMP PUMP. Buy Open Workbench Logic Sniffer [OBC101E1P. Basil Watson | 2012-09-02 Intermittent Logic Sniffer I purchased unit ver 1.01 some time back . It worked for about a year. It now works very intermittently. I have tried loading all version of firmware but no success. Hi,you can sent e-mail to jack.gassett@nospam@gadgetfactory.net(the designer of this project).And thank you for your understanding. Answered by Jacket Chueng | 2012-09-05 Was this useful? Open Bench Logic Sniffer "case"

The Open Bench Logic Analyser is a cheap ($50) open source logic analyser board, which talks a standard (ie open) protocol to a PC client.

Very useful! As it's just a bare board, lots of people have designed and build their own case for it. Many are built with 3d printers and related methods. I did one too, but instead of going the real high tech route, I just used a slab of 6mm Perspex, cut into 3 pieces and with slots milled for the PCB to slide into. Check it out: Open Workbench Logic Sniffer First Impressions « Silly Science. A while ago I spotted the Open Workbench Logic Sniffer on Hackaday.

A logic sniffer . analyser is a useful tool have around the place and at ~$50 with some flying leads to make it up to the free shipping threshold. Seeing as it arrived the other day I thought I would share my first impressions of it... The Board The system comes shipped as a bare board - so I need to get some self adhesive rubber feet for it really - I will also keep my eye out for a potential case as well. 17 Channel Logic Analyzer.

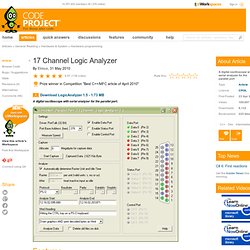

Download LogicAnalyzer 1.5 - 1.73 MB A digital oscilloscope with serial analyzer for the parallel port.

Features Digital Oscilloscope / Logic Analyzer with up to 17 input lines Uses the parallel (printer) port for input. While Logic Analyzers normally are very expensive, this one is for zero cost Written in speed optimized C++ to get the maximum possible sample rates The program is a stand alone single EXE file which neither needs any additional DLLs nor any framework. Versions. Open Bench Logic Sniffer.