Vivado Design Suite. Vivado Implementation. In today’s technology nodes (28nm and below), interconnect is the bottleneck for high performance and high density designs.

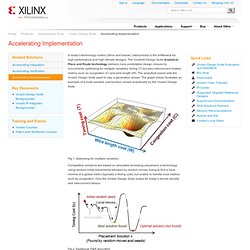

The Vivado® Design Suite Analytical Place and Route technology delivers more predictable design closure by concurrently optimizing for multiple variables: timing (T) but also interconnect related metrics such as congestion (C) and wire length (W). The analytical placer sets the Vivado Design Suite apart to stay a generation ahead. The graph below illustrates an example of a multi-variable cost function solved analytically by the Vivado Design Suite. Fig.1 Optimizing for multiple variables Competitive solutions are based on simulated annealing placement, a technology using random initial placements followed by random moves, trying to find a local minima of a global metric (typically a timing cost), but unable to handle local metrics such as congestion.

Fig.2 Traditional P&R Algorithm 4X Faster Implementation 20% Better Device Utilization Fig. 5 35% Lower Power. Verification and Debug. Integrated Cockpit for Design and Simulation The Vivado® Design Suite employs a shared, scalable data model to accommodate the largest programmable logic devices.

This single data model is used throughout the implementation process, enabling users to gain visibility into key design metrics such as timing, power, resource utilization, and routing congestion much earlier in the design process. These estimates become progressively more accurate throughout the design flow, enabling faster design closure with fewer iterations. Vivado Integration. Block-based IP Integration with Vivado IP Integrator The Vivado® Design Suite shatters the RTL design productivity plateau by providing the industry’s first plug-and-play IP integration design environment, with its IP Integrator feature.

Vivado IP Integrator provides a graphical and Tcl-based, correct-by-construction design development flow. It provides a device and platform aware, interactive environment that supports intelligent auto-connection of key IP interfaces, one-click IP subsystem generation, real-time DRCs, and interface change propagation, combined with a powerful debug capability. Designers work at the “interface” and not “signal” level of abstraction when making connections between IP, greatly increasing productivity. Often times this is using industry standard AXI4 interfaces, but dozens of other interfaces are also supported by IP integrator. Product Support & Documentation. Wp416-Vivado-Design-Suite. Vivado_Product_Brief. Embedded Tools and IP Cores.

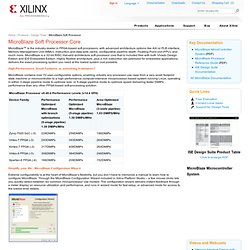

MicroBlaze Soft Processor. MicroBlaze Soft Processor Core MicroBlaze™ is the industry-leader in FPGA-based soft processors, with advanced architecture options like AXI or PLB interface, Memory Management Unit (MMU), instruction and data-side cache, configurable pipeline depth, Floating-Point unit (FPU), and much more.

MicroBlaze is a 32-bit RISC Harvard architecture soft processor core that is included free with both Vivado Design Edition and IDS Embedded Edition. Highly flexible architecture, plus a rich instruction set optimized for embedded applications, delivers the exact processing system you need at the lowest system cost possible. High-Performance, Small Footprint, or something In-between? Simplify your life - MicroBlaze Configuration Wizard Extreme configurability is at the heart of MicroBlaze’s flexibility, but you don’t have to memorize a manual to learn how to configure MicroBlaze. New version 8 features expand MicroBlaze capabilities even further. Embedded Processing Peripheral IP Cores. Software Development Kit (SDK) The Software Development Kit (SDK) is the Xilinx Integrated Design Environment for creating embedded applications on any of Xilinx' award winning microprocessors from Zynq™-7000 All Programmable SoCs, to the industry-leading MicroBlaze™.

Platform Studio (XPS) Xilinx Platform Studio (XPS) is a key component of the ISE Embedded Edition Design Suite, helping the hardware designer to easily build, connect and configure embedded processor-based systems; from simple state machines to full-blown 32-bit RISC microprocessor systems.

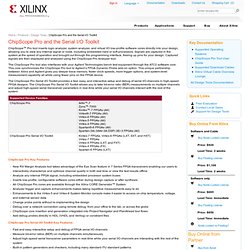

XPS employs graphical design views and sophisticated correct-by-design wizards to guide developers through the steps necessary to create custom processor systems within minutes. The true potential of XPS emerges with its ability to configure and integrate plug and play IP cores from the Xilinx Embedded IP catalog, with custom or 3rd party Verilog and VHDL designs. ChipScope Pro and the Serial I/O Toolkit. ChipScope Pro and the Serial I/O Toolkit ChipScope™ Pro tool inserts logic analyzer, system analyzer, and virtual I/O low-profile software cores directly into your design, allowing you to view any internal signal or node, including embedded hard or soft processors.

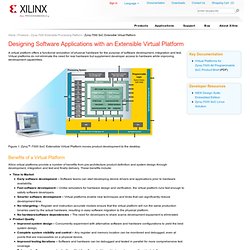

Signals are captured in the system at the speed of operation and brought out through the programming interface, freeing up pins for your design. Captured signals are then displayed and analyzed using the ChipScope Pro Analyzer tool. The ChipScope Pro tool also interfaces with your Agilent Technologies bench test equipment through the ATC2 software core. This core synchronizes the ChipScope Pro tool to Agilent’s FPGA Dynamic Probe add-on option. The ChipScope Pro Serial I/O Toolkit provides a fast, easy, and interactive setup and debug of serial I/O channels in high-speed FPGA designs. Zynq-7000 EPP Virtual Platform. A virtual platform offers a functional simulation of physical hardware for the purpose of software development, integration and test.

Virtual platforms do not eliminate the need for real hardware but supplement developer access to hardware while improving development capabilities. Figure 1: Zynq™-7000 SoC Extensible Virtual Platform moves product development to the desktop. Benefits of a Virtual Platform. QEMU on Zynq. Xilinx actively develops a QEMU tree for both Microblaze and Zynq.

The Xilinx QEMU git tree follows mainline development continuously and developers make effort to push all developments upstream. The Xilinx tree is more however more complete that the qemu upstream ( and it is recommended that customers use the QEMU tree provided at Supported Zynq Hardware A limited subset of the Xilinx Zynq hardware is supported in QEMU. Each model has only been tested with the respective Linux driver such that not all hardware features may be modelled. ISE Software and Design Tools. ISE Simulator (ISim) ISE Simulator (ISim) ISim provides a complete, full-featured HDL simulator integrated within ISE.

HDL simulation now can be an even more fundamental step within your design flow with the tight integration of the ISim within your design environment. ISim Key Features: Mixed language support Supports VHDL-93 and Verilog 2001 Native support for all HardIP blocks PPC, MGT, PCIe, etc. XST Synthesis. XST Synthesis The ISE® Design Suite includes Xilinx Synthesis Technology (XST) allowing synthesis of HDL designs to create Xilinx specific netlist files. With specially optimized algorithms to leverage the advanced architectures of the Xilinx FPGA families, XST offers designers a low-cost design solution to achieve optimal design results. Integrated within the ISE Project Navigator, XST provides support for mixed-language Verilog and VHDL designs. This flexibility allows designers to mix the best possible design source code for any particular project.

XPower Estimator User Guide. System Generator for DSP. System Generator for DSP System Generator for DSP™ is the industry’s leading high-level tool for designing high-performance DSP systems using FPGAs. Develop highly parallel systems with the industry’s most advanced FPGAs Provide system modeling and automatic code generation from Simulink® and MATLAB® (The Mathworks, Inc.) Integrates RTL, embedded, IP, MATLAB and hardware components of a DSP system A key component of the Xilinx DSP Targeted Design Platform.