FPGAs; Lesson 1: Concept Guide and Step by Step Tutorial to Flash LEDs. Verilog HDL BCD 7 Segment in Quartus II. VHDL Basics. VHDL coding tips and tricks: VHDL code for BCD to 7-segment display converter. Here is a program for BCD to 7-segment display decoder.

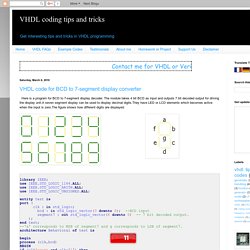

The module takes 4 bit BCD as input and outputs 7 bit decoded output for driving the display unit.A seven segment display can be used to display decimal digits.They have LED or LCD elements which becomes active when the input is zero.The figure shows how different digits are displayed: libraryIEEE;useIEEE.STD_LOGIC_1164.ALL;useIEEE.STD_LOGIC_ARITH.ALL;useIEEE.STD_LOGIC_UNSIGNED.ALL; Welcome To VHDL Page. Details. Preface The following content is pulled directly from the lab report that we wrote describing this project, so if you're having trouble understanding anything here please, please don't hesitate to send me a message and I would be more than happy to explain it on a less technical level!

I did not build this project alone! Much of the design, all of the motor circuit design, all of the Verilog, most of the cable work, and most of the CAD were done by my partner Kyle. I did the primary work on the LED control software and the control board design and population. Overview Persistence of vision (or POV) is the phenomenon by which the eye, seeing a rapidly moving objects, stitches together the object’s position at different times into a single cohesive image. Teledyne DALSA Imaging Blog. Image filters – like Gaussian blurring, median filtering, and morphological operations, are indispensable tools in image pre-processing.

But with the increasing bandwidth requirements today, such pre-processing tasks can be offloaded to a parallel processing hardware monster known as an FPGA (Field Programmable Gate Array). FPGAs are reconfigurable devices that contain small Look-Up Tables (LUTs), small memories (Registers), larger block RAM (BRAM), and dedicated multipliers. The user basically programs the connections and parameters for these blocks. FPGAs excel in high parallel processing tasks and, although they typically operate at lower frequencies than CPUs, for a given task they can easily outperform a CPU by orders of magnitude.

OpenCores. FPGA course. From Hamsterworks Wiki!

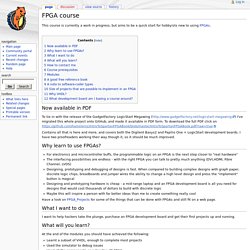

This course is currently a work in progress, but aims to be a quick start for hobbyists new to using FPGAs. Now available in PDF To tie in with the release of the GadgetFactory LogicStart Megawing ( I've migrated this whole project onto GitHub, and made it available in PDF form. To download the full PDF click on Contains all that is here and more, and covers both the Digilent Basys2 and Papilio One + LogicStart development boards. Why learn to use FPGAs? Final Projects ECE 5760. FPGA Center - Everthing About FPGA. FPGA Projects. From Hamsterworks Wiki!

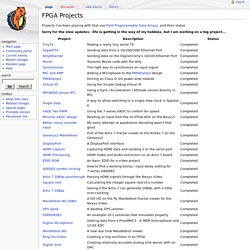

Projects I've been playing with that use Field Programmable Gate Arrays, and their status Sorry for the slow updates - life is getting in the way of my hobbies, but I am working on a big project... There is also a whole lot of mini projects on the Papilio Plus page, for testing interfaces. Unless any of the source files from this site contains headers that indicate otherwise (e.g.in 'CoreGen' components), all of this code is released under the BSD/MIT - Feel free to do anything you want with it. If you would like this disclaimer added to any particular file then please let me know and I will add it for you.

LOGI-BONE. FPGA RGB Matrix. Conseil pour débuter avec la programmation de FPGA. Voilà, étant un programmeur plutôt bas niveau, C et assembleur, j'aimerais descendre encore plus bas et me mettre à la programmation de FPGA.

J'ai déjà d'ailleurs brièvement expérimenté une programmation un peu différente en m'essayant à CUDA (sapusaypalibre donc je ne m'y suis pas attardé, j'y jetterais sûrement à nouveau un oeil quand/si on aura un jour une implémentation libre d'OpenCL sur notre manchot) mais bizarrement aussi bien dans mon cursus universitaire que professionnel je n'ai jamais eu l'occasion de m'y mettre. J'ai donc décidé de combler par moi même cette lacune. LED glow. » Technical details RoseAce. The device had to be able to display a stream of at least 256×256 pixels @ 25 frames per second, with each pixel coded on 24 bits – allowing for more than 4 millions colors.

A Gumstix Overo module with integrated Wifi receives a video stream, eventually rescales it with MPlayer, adjusts brightness / contrast / gamma parameters, and sends it to an Altera Cyclone III FPGA (EP3C25) through an home made MPlayer output plugin. The FPGA acts mainly as a video card. The video stream from the Gumstix is double-buffered in two synchronous SRAM : during one rotation, a frame of the incoming video stream is stored in one of the SRAM, as the other SRAM is read by the FPGA to feed the LED drivers.

At the end of the rotation, both RAM are exchanged and the FPGA signals to the Gumstix that it can begin feeding the next frame. The data rate between the Gumstix and FPGA is roughly 5MB/s. The FPGA also computes the blade position in real time. Design a Handheld POV - An Introduction To CPLD And FPGA - PyroEDU. FPGA programming, where to begin.