Reading Cache Memory. Reading Cache Memory Name: Kamal D.

Status: Other Age: 20s Location: N/A Country: N/A Date: Around 2001 Question: How can we read and store data from cache memory of processor? -Is this thing is possible in java or in VB-6.0 through win32 api Replies: If you read and store any data at all, it will, at some point be read and stored by the cache memory of the processor. If you wish to use the cache as "extra memory" for your data, this is not how the cache works, and not what it was designed for. As far as directly controlling the cache, there are not generally instructions in the processor for doing this. It is possible to optimize the execution speed of a program by arranging your code for optimal use of the cache, but as I will attempt to explain below, it is generally a waste of time, unless you simply want to know. For Java, this is a pointless exercise. VB 6.0 is a little better in that is is compiled, and at least the executable code does go directly to the processor. 1. 2. 3. 4. 5. 6.

Memory part 2: CPU caches. October 1, 2007 This article was contributed by Ulrich Drepper [Editor's note: This is the second installment in Ulrich Drepper's "What every programmer should know about memory" document.

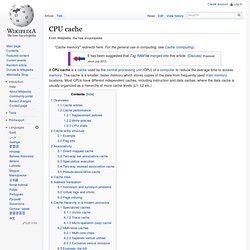

Those who have not read the first part will likely want to start there. CPU cache. Overviews[edit] When the processor needs to read from or write to a location in main memory, it first checks whether a copy of that data is in the cache.

If so, the processor immediately reads from or writes to the cache, which is much faster than reading from or writing to main memory. Most modern desktop and server CPUs have at least three independent caches: an instruction cache to speed up executable instruction fetch, a data cache to speed up data fetch and store, and a translation lookaside buffer (TLB) used to speed up virtual-to-physical address translation for both executable instructions and data. DDR2 SDRAM. PC2-6400 DDR2 SO-DIMM (for notebooks) DDR2 SDRAM is a double data rate synchronous dynamic random-access memory interface.

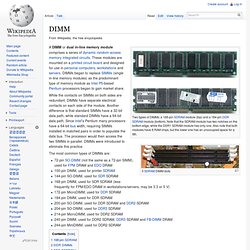

It superseded the original DDR SDRAM specification, and has since been superseded by DDR3 SDRAM. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. DIMM. Two types of DIMMs: a 168-pin SDRAM module (top) and a 184-pin DDR SDRAM module (bottom).

Note that the SDRAM module has two notches on the bottom edge, while the DDR1 SDRAM module has only one. Also note that both modules have 8 RAM chips, but the lower one has an unoccupied space for a 9th. While the contacts on SIMMs on both sides are redundant, DIMMs have separate electrical contacts on each side of the module. DDR SDRAM和SDR SDRAM的区别. CPU cache. Overviews[edit] When the processor needs to read from or write to a location in main memory, it first checks whether a copy of that data is in the cache.

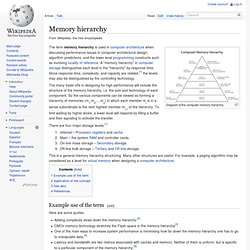

If so, the processor immediately reads from or writes to the cache, which is much faster than reading from or writing to main memory. Memory hierarchy. Diagram of the computer memory hierarchy The term memory hierarchy is used in computer architecture when discussing performance issues in computer architectural design, algorithm predictions, and the lower level programming constructs such as involving locality of reference.

A "memory hierarchy" in computer storage distinguishes each level in the "hierarchy" by response time. Since response time, complexity, and capacity are related,[1] the levels may also be distinguished by the controlling technology. The many trade-offs in designing for high performance will include the structure of the memory hierarchy, i.e. the size and technology of each component. So the various components can be viewed as forming a hierarchy of memories (m1,m2,... There are four major storage levels.[1] Internal – Processor registers and cache.Main – the system RAM and controller cards.On-line mass storage – Secondary storage.Off-line bulk storage – Tertiary and Off-line storage.

Example use of the term[edit] Cache. From Wikipedia, the free encyclopedia. Computer data storage. 40 GBPATA hard disk drive (HDD); when connected to a computer it serves as secondary storage. 160 GB SDLT tape cartridge, an example of off-line storage.

When used within a robotic tape library, it is classified as tertiary storage instead. Functionality[edit] Data organization and representation[edit] Data compression methods allow in many cases to represent a string of bits by a shorter bit string ("compress") and reconstruct the original string ("decompress") when needed. For security reasons certain types of data (e.g., credit-card information) may be kept encrypted in storage to prevent the possibility of unauthorized information reconstruction from chunks of storage snapshots.

Hierarchy of storage[edit] DDR. DDR is the German acronym for Deutsche Demokratische Republik (German) or German Democratic Republic (English), a former state in Europe, 1949–1990.

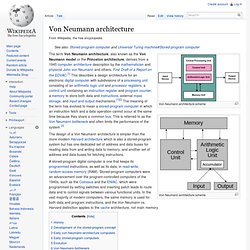

It is also referred to as East Germany. DDR may also refer to: In politics: In science: In technology: Von Neumann architecture. Von Neumann architecture scheme The design of a Von Neumann architecture is simpler than the more modern Harvard architecture which is also a stored-program system but has one dedicated set of address and data buses for reading data from and writing data to memory, and another set of address and data buses for fetching instructions.

A stored-program digital computer is one that keeps its programmed instructions, as well as its data, in read-write, random-access memory (RAM). Stored-program computers were an advancement over the program-controlled computers of the 1940s, such as the Colossus and the ENIAC, which were programmed by setting switches and inserting patch leads to route data and to control signals between various functional units. In the vast majority of modern computers, the same memory is used for both data and program instructions, and the Von Neumann vs. Harvard distinction applies to the cache architecture, not main memory. History[edit] Independently, J.